728x90

728x90

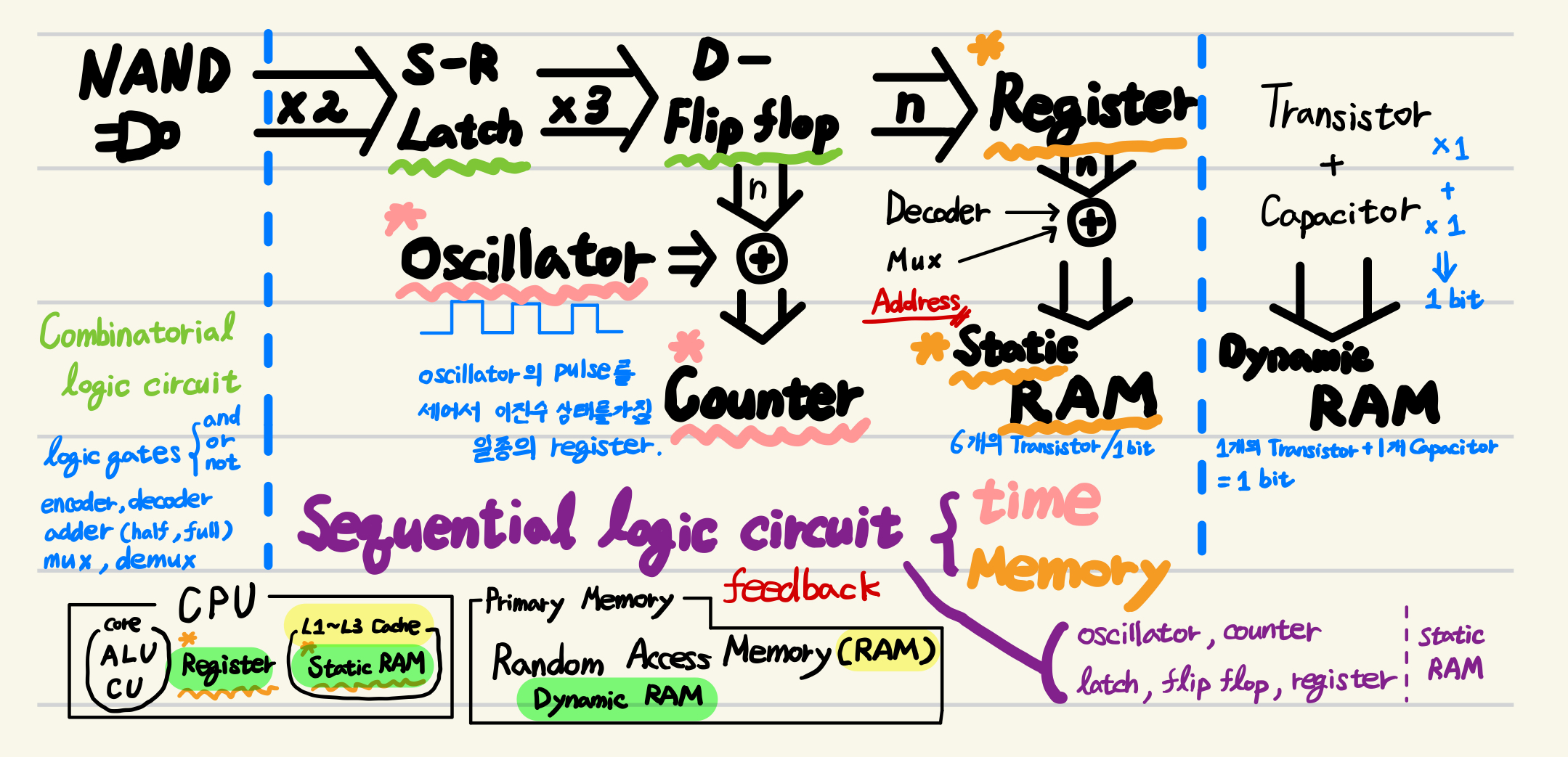

Sequential Logic Circuit (순차 논리 회로):

Sequtial Logic Circuit:

- 시간(time), 메모리(memory), 피드백 루프(feedback loop)를 갖춘 회로.

- time: oscillator, counter

- memory: latch, flip-flop, register, SRAM

- Combinatorial Logic Circuit (조합 논리 회로)와 달리 과거의 입력과 출력이 현재의 출력에 영향을 미치는 특성.

- 같은 입력이라도 이전 상태에 따른 다른 출력 생성.

2025.03.25 - [Computer/CE] - [CE] Sequential Logic Circuit

[CE] Sequential Logic Circuit

Sequential Logic Circuit(순차논리회로)Sequential Logic Circuit(순차논리회로)는 디지털 회로의 한 종류로,현재의 입력뿐만 아니라이전 상태(과거 입력)에 따라 출력이 결정되는 회로를 가리킴.이전 상태에

dsaint31.tistory.com

주요 구성 요소:

- 발진기(Oscillator):

- 일정한 주기로 clock(클럭) 신호를 생성하는 타이밍 제어 회로.

- Rectangular Pulse

- 카운터(Counter):

- Oscillator의 clock pulse 를 세어 이진수 형태로 저장하는 일종의 상태 변화 회로.

- clock pulse 를 세는 특수한 register라고 볼 수 있음.

- 두 가지 주요 유형 존재.

- 비동기식(Asynchronous) 카운터:

- Flip-flop들을 캐스케이드(cascade) 방식으로 연결한 구조.

- 한 Flip-flop의 출력이 다음 Flip-flop의 클럭 입력을 구동하는 직렬 연결 방식.

- Ripple Counter라고도 불리며 신호 지연 발생 (Propagation Delay).

- 동기식(Synchronous) 카운터:

- 모든 Flip-flop들이 단일 공통 clock에 의해 동시에 구동되는 구조.

- 병렬 연결 방식으로 신호 지연이 적고 고주파수 동작 가능.

- 비동기식(Asynchronous) 카운터:

- Example: 프로그램 카운터(Program Counter, PC)

- 다음에 실행할 명령어의 주소를 저장하는 특수 카운터.

- 명령어 실행 순서 제어 역할.

- 래치(Latch):

- 입력 신호 activation level 동안의 데이터를 저장하는 기본 메모리 소자.

- 제어 신호에 따른 데이터 상태 유지 기능.

- Example: SR Latch = 2개의 NAND.

- 플립플롭(Flip-flop):

- Clock(클럭) 신호의 특정 Edge(에지)에서만 상태를 변화시키는 안정적 메모리 소자.

- 정확한 타이밍 제어 메커니즘이 가능함: Latch의 경우 level 이 유지되는 동안 입력값이 변경될 수 있으나 flip-flop은 그런 문제가 없음.

- 단, setup 및 hold time 동안은 유지되어야 함.

- Example: D Flip-flop = 3개의 SR Latch.

- 레지스터(Register):

- 여러 flip-flop 을 병렬로 묶어서 각 bit가 독립적으로 데이터를 저장하는 회로.

- 모든 flip-flop이 동일한 클럭에 의해 동시에 구동되는 동기식 구조.

- 동시 데이터 입출력 가능.

- CPU 내부에서 사용되는 가장 빠른 메모리 소자 (단 비트별 가장 비싼 단가를 보임)

- 정적 RAM(Static RAM):

- 전원 공급 동안 데이터를 유지(volatile)하는 flip-flop 기반 메모리 셀 구조.

- 1bit : 6개의 transistors (=1개의 flip-flop)

- Latch(래치), Flip-flop(플립플롭), Register(레지스터)와 달리 주소(address) 기반 접근 방식: Random Access

- 디코더(decoder)를 이용하여 특정 행(row)을 선택하고, 멀티플렉서(multiplexer)를 통해 특정 열(column)을 선택하는 매트릭스 구조 - Register Pile에서 Address 통해 특정 register를 선택한다고 생각할 수 있음.

- 이러한 address(주소) 지정 방식으로 대규모 메모리 셀 어레이에서 특정 위치의 데이터에 대한 Random Access (임의 접근) 가능성.

- 전원 공급 동안 데이터를 유지(volatile)하는 flip-flop 기반 메모리 셀 구조.

같이보면 좋은 자료

https://dsaint31.me/mkdocs_site/CE/ch03_seq/ce03_01_0_0_memory0/

BME

시간 및 기억소자들 Combinatorial Logic과 달리, Sequential Logic의 경우 과거의 출력값에도 영향을 받기 때문(feedback)에 Memory Device가 필요 또한, 현재의 input 이외의 과거 상태 및 현재 상태 값들을 고려

dsaint31.me

BME

Memory (기억장치) 컴퓨터는 어찌보면 입력된 데이터들을 처리하고 그 결과를 출력하는 장치 임. 데이터 처리는 데이터 등에 해당하는 여러 bit를 조작해야만 하며, 이들을 저장할 장소가 필연적으

dsaint31.me

728x90

'Computer > CE' 카테고리의 다른 글

| [CE] Sequential Logic Circuit (0) | 2025.03.25 |

|---|---|

| [Ex] CMRR 및 특정 CMRR에서의 최소 신호값 구하기. (0) | 2025.03.25 |

| [CE] 오늘날의 VLSI 분류 (0) | 2025.03.25 |

| [CE] Linear Search, Naive Search, Brute Force Search (0) | 2024.11.16 |

| [CE] Queue (1) | 2024.11.09 |